在电子束曝光与离子注入工艺的结合研究中,科研团队探索了高精度掺杂区域的制备技术。离子注入的掺杂区域需要与器件图形精确匹配,团队通过电子束曝光制备掩模图形,控制离子注入的区域与深度,研究不同掺杂浓度对器件电学性能的影响。在 IGZO 薄膜晶体管的研究中,优化后的曝光与注入工艺使器件的沟道导电性调控精度得到提升,为器件性能的精细化调节提供了可能。这项研究展示了电子束曝光在半导体掺杂工艺中的关键作用。通过汇总不同科研机构的工艺数据,分析电子束曝光关键参数的合理范围,为制定行业标准提供参考。在内部研究中,团队已建立一套针对第三代半导体材料的电子束曝光在超高密度存储领域实现纳米全息结构的精确编码。四川纳米器件电子束曝光加工

针对电子束曝光在教学与人才培养中的作用,研究所利用该技术平台开展实践培训。作为拥有人才团队的研究机构,团队通过电子束曝光实验课程,培养研究生与青年科研人员的微纳加工技能,让学员参与从图形设计到曝光制备的全流程操作。结合第三代半导体器件的研发项目,使学员在实践中掌握曝光参数优化与缺陷分析的方法,为宽禁带半导体领域培养了一批具备实际操作能力的技术人才。研究所展望了电子束曝光技术与第三代半导体产业发展的结合前景,制定了中长期研究规划。随着半导体器件向更小尺寸、更高集成度发展,电子束曝光的纳米级加工能力将发挥更重要作用,团队计划在提高曝光速度、拓展材料适用性等方面持续攻关。结合省级重点科研项目的支持,未来将重点研究电子束曝光在量子器件、高频功率器件等领域的应用,通过与产业界的深度合作,推动科研成果向实际生产力转化,助力广东半导体产业的技术升级。四川纳米器件电子束曝光加工电子束曝光为光学微腔器件提供亚波长精度的定制化制备解决方案。

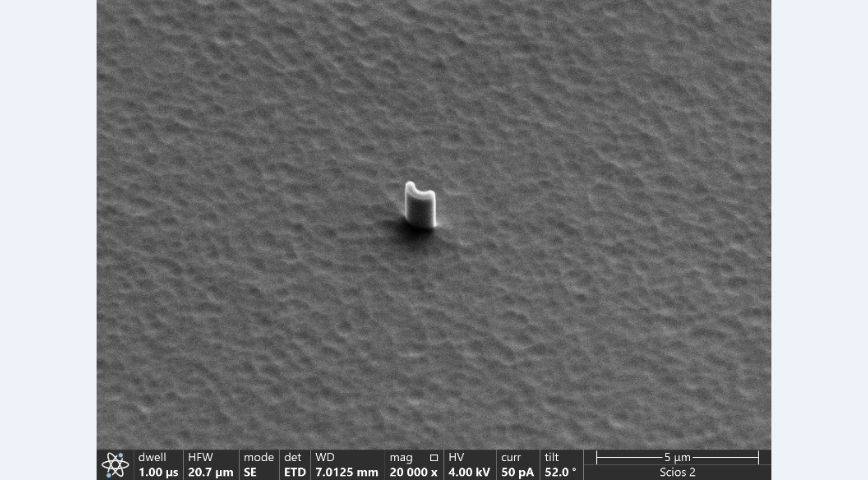

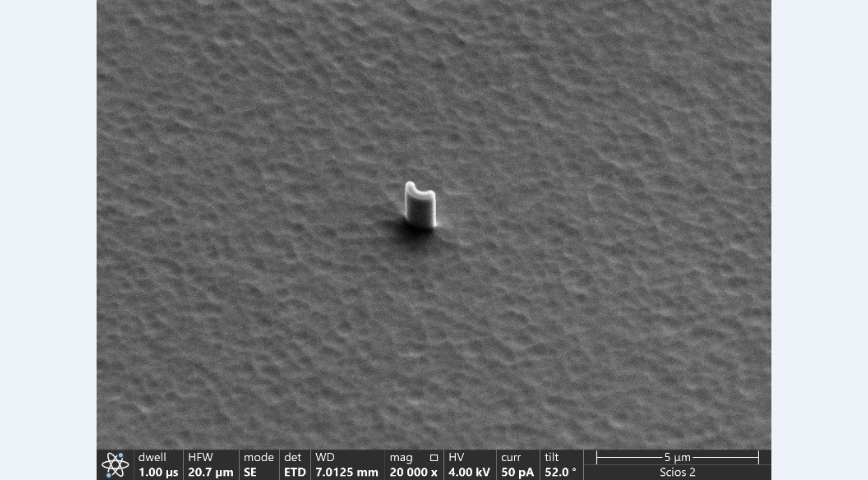

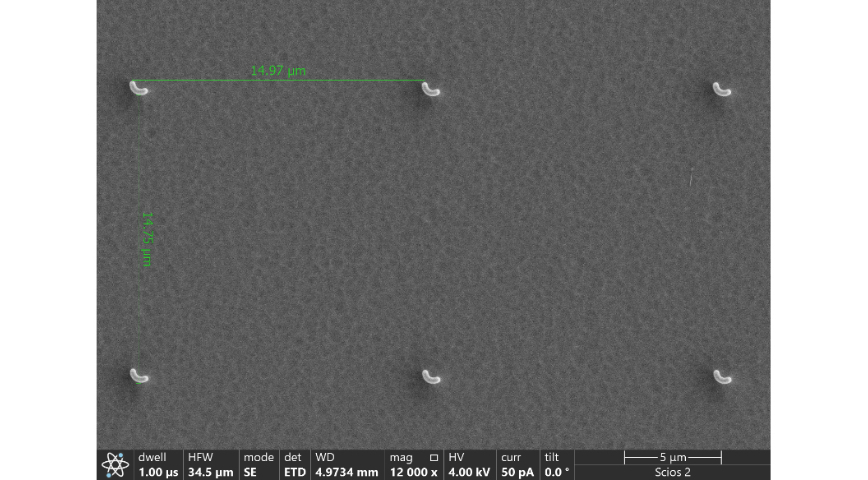

围绕电子束曝光的套刻精度控制,科研团队开展了系统研究。在多层结构器件的制备中,各层图形的对准精度直接影响器件性能,团队通过改进晶圆定位系统与标记识别算法,将套刻误差控制在较小范围内。依托材料外延平台的表征设备,可精确测量不同层间图形的相对位移,为套刻参数的优化提供量化依据。在第三代半导体功率器件的研发中,该技术确保了源漏电极与沟道区域的精细对准,有效降低了器件的接触电阻,相关工艺参数已纳入中试生产规范。

研究所利用电子束曝光技术制备微纳尺度的热管理结构,探索其在功率半导体器件中的应用。功率器件工作时产生的热量需快速散出,团队通过电子束曝光在器件衬底背面制备周期性微通道结构,增强散热面积。结合热仿真与实验测试,分析微通道尺寸与排布方式对散热性能的影响,发现特定结构的微通道能使器件工作温度降低一定幅度。依托材料外延平台,可在制备散热结构的同时保证器件正面的材料质量,实现散热与电学性能的平衡,为高功率器件的热管理提供了新解决方案。电子束曝光利用非光学直写原理突破光学衍射极限,实现纳米级精度加工和复杂图形直写。

研究所针对电子束曝光在大面积晶圆上的均匀性问题开展研究。由于电子束在扫描过程中可能出现能量衰减,6 英寸晶圆边缘的图形质量有时会与中心区域存在差异,科研团队通过分区校准曝光剂量的方式,改善了晶圆面内的曝光均匀性。利用原子力显微镜对晶圆不同区域的图形进行表征,结果显示优化后的工艺使边缘与中心的线宽偏差控制在较小范围内。这项研究提升了电子束曝光技术在大面积器件制备中的适用性,为第三代半导体中试生产中的批量一致性提供了保障。该所承担的省级项目中,电子束曝光用于芯片精细图案制作。四川纳米器件电子束曝光加工

电子束刻蚀推动人工视觉芯片的光电转换层高效融合。四川纳米器件电子束曝光加工

电子束曝光颠覆传统制冷模式,在半导体制冷片构筑量子热桥结构。纳米级界面声子工程使热电转换效率提升三倍,120W/cm²热流密度下维持芯片38℃恒温。在量子计算机低温系统中替代液氦制冷,冷却能耗降低90%。模块化设计支持三维堆叠,为10kW级数据中心机柜提供零噪音散热方案。电子束曝光助力深空通信升级,为卫星激光网络制造亚波长光学器件。8级菲涅尔透镜集成波前矫正功能,50000公里距离光斑扩散小于1米。在北斗四号星间链路系统中,数据传输速率达100Gbps,误码率小于10⁻¹⁵。智能热补偿机制消除太空温差影响,保障十年在轨无性能衰减。四川纳米器件电子束曝光加工