围绕电子束曝光在第三代半导体功率器件栅极结构制备中的应用,科研团队开展了专项研究。功率器件的栅极尺寸与形状对其开关性能影响明显,团队通过电子束曝光制备不同线宽的栅极图形,研究尺寸变化对器件阈值电压与导通电阻的影响。利用电学测试平台,对比不同栅极结构的器件性能,优化出适合高压应用的栅极尺寸参数。这些研究成果已应用于省级重点科研项目中,为高性能功率器件的研发提供了关键技术支撑。科研人员研究了电子束曝光过程中的电荷积累效应及其应对措施。绝缘性较强的半导体材料在电子束照射下容易积累电荷,导致图形偏移或畸变,团队通过在曝光区域附近设置导电辅助层与接地结构,加速电荷消散。电子束刻蚀为量子离子阱系统提供高精度电极阵列。甘肃套刻电子束曝光多少钱

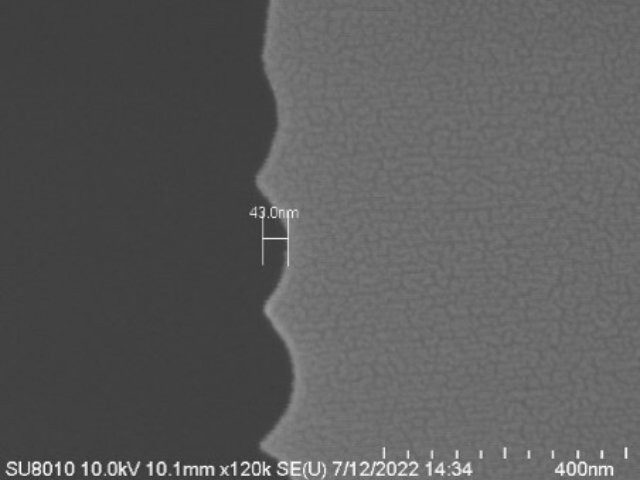

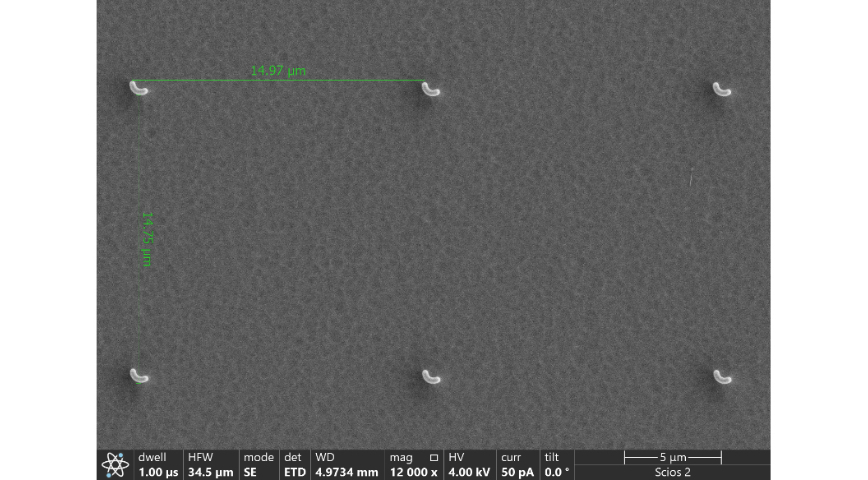

电子束曝光中的新型抗蚀剂如金属氧化物(氧化铪)正面临性能挑战。其高刻蚀选择比(硅:100:1)但灵敏度为10mC/cm²。研究通过铈掺杂和预曝光烘烤(180°C/2min)提升氧化铪胶灵敏度至1mC/cm²,图形陡直度达89°±1。在5纳米节点FinFET栅极制作中,电子束曝光应用这类抗蚀剂减少刻蚀工序,平衡灵敏度和精度需求。操作电子束曝光时,基底导电处理是关键步骤:绝缘样品需旋涂50nm导电聚合物(如ESPACER300Z)以防电荷累积。热漂移控制通过±0.1℃恒温系统和低温样品台实现。大尺寸拼接采用激光定位反馈策略,如100μm区域分9次曝光(重叠10μm),将套刻误差从120nm降至35nm。优化参数包括剂量分区和扫描顺序设置。安徽微纳光刻电子束曝光工艺电子束曝光在超高密度存储领域实现纳米全息结构的精确编码。

科研团队探索电子束曝光与化学机械抛光技术的协同应用,用于制备全局平坦化的多层结构。多层器件在制备过程中易出现表面起伏,影响后续曝光精度,团队通过电子束曝光定义抛光阻挡层图形,结合化学机械抛光实现局部区域的精细平坦化。对比传统抛光方法,该技术能使多层结构的表面粗糙度降低一定比例,为后续曝光工艺提供更平整的基底。在三维集成器件的研究中,这种协同工艺有效提升了层间对准精度,为高密度集成器件的制备开辟了新路径,体现了多工艺融合的技术创新思路。

研究所针对电子束曝光在大面积晶圆上的均匀性问题开展研究。由于电子束在扫描过程中可能出现能量衰减,6 英寸晶圆边缘的图形质量有时会与中心区域存在差异,科研团队通过分区校准曝光剂量的方式,改善了晶圆面内的曝光均匀性。利用原子力显微镜对晶圆不同区域的图形进行表征,结果显示优化后的工艺使边缘与中心的线宽偏差控制在较小范围内。这项研究提升了电子束曝光技术在大面积器件制备中的适用性,为第三代半导体中试生产中的批量一致性提供了保障。电子束曝光为光学微腔器件提供亚波长精度的定制化制备解决方案。

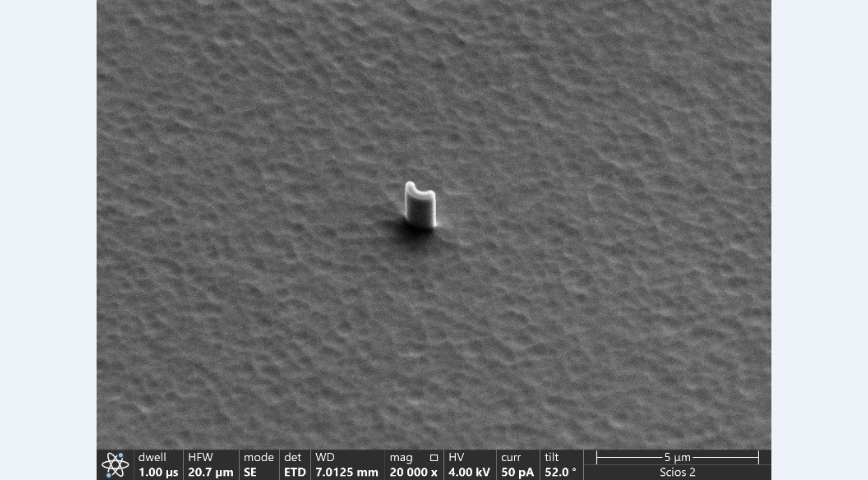

现代科研平台将电子束曝光模块集成于扫描电子显微镜(SEM),实现原位加工与表征。典型应用包括在TEM铜网制作10μm支撑膜窗口或在AFM探针沉积300纳米铂层。利用二次电子成像和能谱(EDS)联用,电子束曝光支持实时闭环操作(如加工后成分分析),提升跨尺度研究效率5倍以上。其真空兼容性和定位精度使纳米实验室成为材料科学关键工具。在电子束曝光的矢量扫描模式下,剂量控制是主要参数(剂量=束流×驻留时间/步进)。典型配置如100kV加速电压下500pA束流对应3纳米束斑,剂量范围100-2000μC/cm²。采用动态剂量调制和邻近效应矫正(如灰度曝光),可将线边缘粗糙度降至1nmRMS。套刻误差依赖激光干涉仪实时定位技术,精度达±35nm/100mm,确保图形保真度。电子束曝光支持深空探测系统在极端环境下的高效光能转换方案。上海套刻电子束曝光技术

电子束曝光在微型热电制冷器领域突破界面热阻控制瓶颈。甘肃套刻电子束曝光多少钱

在电子束曝光与离子注入工艺的结合研究中,科研团队探索了高精度掺杂区域的制备技术。离子注入的掺杂区域需要与器件图形精确匹配,团队通过电子束曝光制备掩模图形,控制离子注入的区域与深度,研究不同掺杂浓度对器件电学性能的影响。在 IGZO 薄膜晶体管的研究中,优化后的曝光与注入工艺使器件的沟道导电性调控精度得到提升,为器件性能的精细化调节提供了可能。这项研究展示了电子束曝光在半导体掺杂工艺中的关键作用。通过汇总不同科研机构的工艺数据,分析电子束曝光关键参数的合理范围,为制定行业标准提供参考。在内部研究中,团队已建立一套针对第三代半导体材料的甘肃套刻电子束曝光多少钱