刻蚀在半导体器件加工中的应用非常普遍。例如,在集成电路制造中,刻蚀用于形成晶体管的栅极、源极和漏极等结构;在光学器件制造中,刻蚀用于形成光波导、光栅等结构;在传感器制造中,刻蚀用于制备纳米结构的敏感层等。刻蚀技术的发展对半导体器件的制造和性能提升起到了重要的推动作用。随着半导体器件的不断发展,对刻蚀技术的要求也越来越高,如刻蚀速度的提高、刻蚀深度的控制、刻蚀剂的选择等。因此,刻蚀技术的研究和发展仍然是一个重要的课题,将继续推动半导体器件的进一步发展。二极管的主要原理就是利用PN结的单向导电性,在PN结上加上引线和封装就成了一个二极管。湖南5G半导体器件加工平台

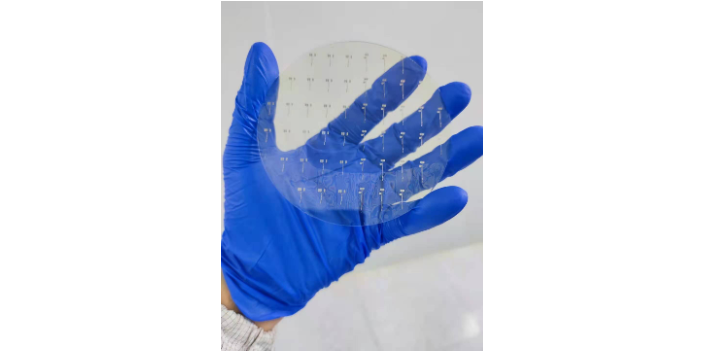

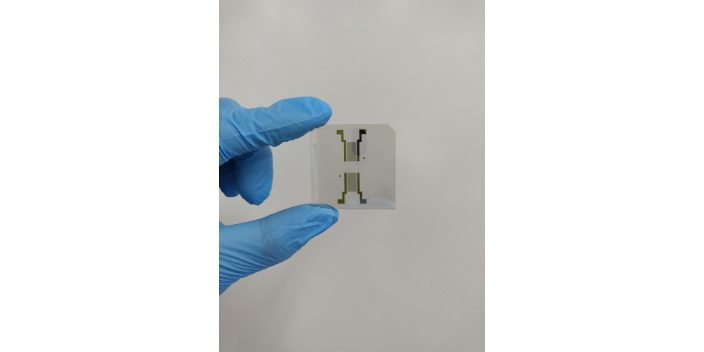

半导体器件加工是指将半导体材料加工成具有特定功能的器件的过程。它是半导体工业中非常重要的一环,涉及到多个步骤和工艺。下面将详细介绍半导体器件加工的步骤。蚀刻:蚀刻是将光刻图案转移到晶圆上的关键步骤。蚀刻是利用化学反应将不需要的材料从晶圆表面去除的过程。常用的蚀刻方法包括湿蚀刻和干蚀刻。沉积:沉积是在晶圆表面上形成薄膜的过程。沉积可以通过物理的气相沉积(PVD)、化学气相沉积(CVD)、溅射沉积等方法实现。沉积的薄膜可以用于形成导电层、绝缘层或金属层等。半导体器件加工厂商退火是指加热离子注入后的硅片,修复离子注入带来的晶格缺陷的过程。

半导体技术材料问题:电子组件进入纳米等级后,在材料方面也开始遭遇到一些瓶颈,因为原来使用的材料性能已不能满足要求。很简单的一个例子,是所谓的闸极介电层材料;这层材料的基本要求是要能绝缘,不让电流通过。使用的是由硅基材氧化而成的二氧化硅,在一般状况下这是一个非常好的绝缘材料。但因组件的微缩,使得这层材料需要越做越薄。在纳米尺度时,如果继续使用这个材料,这层薄膜只能有约 1 纳米的厚度,也就是 3 ~ 4 层分子的厚度。但是在这种厚度下,任何绝缘材料都会因为量子穿隧效应而导通电流,造成组件漏电,以致失去应有的功能,因此只能改用其它新材料。但二氧化硅已经沿用了三十多年,几乎是集各种优点于一身,这也是使硅能够在所有的半导体中脱颖而出的关键,要找到比它功能更好的材料与更合适的制作方式,实在难如登天。

半导体制程是一项复杂的制作流程,先进的 IC 所需要的制作程序达一千个以上的步骤。这些步骤先依不同的功能组合成小的单元,称为单元制程,如蚀刻、微影与薄膜制程;几个单元制程组成具有特定功能的模块制程,如隔绝制程模块、接触窗制程模块或平坦化制程模块等;然后再组合这些模块制程成为某种特定 IC 的整合制程。大约在 15 年前,半导体开始进入次微米,即小于微米的时代,尔后更有深次微米,比微米小很多的时代。到了 2001 年,晶体管尺寸甚至已经小于 0.1 微米,也就是小于 100 纳米。刻蚀是与光刻相联系的图形化处理的一种主要工艺。

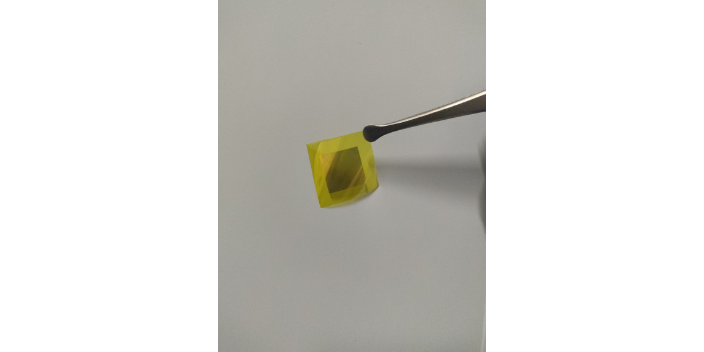

随着科技的不断进步和市场需求的不断变化,半导体器件加工也在不断发展和创新。未来发展方向主要包括以下几个方面:三维集成:目前的半导体器件加工主要是在二维平面上进行制造,但随着技术的发展,人们对三维集成的需求也越来越高。三维集成可以提高器件的性能和功能,同时减小器件的尺寸。未来的半导体器件加工将会更加注重三维集成的研究和开发,包括通过垂直堆叠、通过硅中间层连接等方式实现三维集成。新材料的应用:随着半导体器件加工的发展,人们对新材料的需求也越来越高。而新材料可以提供更好的性能和更低的功耗,同时也可以拓展器件的应用领域。未来的半导体器件加工将会更加注重新材料的研究和应用,如石墨烯、二硫化钼等。半导体器件加工要考虑器件的故障排除和维修的问题。福建5G半导体器件加工工厂

单晶圆清洗取代批量清洗是先进制程的主流,单晶圆清洗通常采用单晶圆清洗设备。湖南5G半导体器件加工平台

半导体技术材料问题:而且,材料是组件或 IC 的基础,一旦改变,所有相关的设备与后续的流程都要跟着改变,真的是牵一发而动全身,所以半导体产业还在坚持,不到后面一刻肯定不去改变它。这也是为什么 CPU 会越来越烫,消耗的电力越来越多的原因。因为CPU 中,晶体管数量甚多,运作又快速,而每一个晶体管都会「漏电」所造成。这种情形对桌上型计算机可能影响不大,但在可携式的产品如笔记型计算机或手机,就会出现待机或可用时间无法很长的缺点。也因为这样,许多学者相继提出各种新颖的结构或材料,例如利用自组装技术制作纳米碳管晶体管,想利用纳米碳管的优异特性改善其功能或把组件做得更小。但整个产业要做这么大的更动,在实务上是不可行的,顶多只能在特殊的应用上,如特殊感测组件,找到新的出路。湖南5G半导体器件加工平台