FPGA 定制项目之消费电子无线耳机降噪模块开发某音频设备厂商需定制 FPGA 无线耳机降噪模块,用于主动降噪耳机,要求支持混合降噪(前馈 + 反馈),降噪深度大于 25dB,适配 20-2000Hz 噪音频段,且功耗控制在 8mW 以内。项目团队选用 Lattice MachXO3 系列 FPGA,其低功耗与快速信号处理能力适配耳机便携需求。FPGA 接收前馈麦克风与反馈麦克风采集的噪音信号,通过自适应滤波算法生成反向降噪信号,与音频信号叠加实现降噪效果。硬件设计采用微型封装,减少模块体积;软件层面优化算法复杂度,降低功耗。测试中,模块在地铁、街道等场景降噪深度达 28dB,20-2000Hz 频段内噪音抑制效果均匀,连续工作 12 小时消耗耳机 5% 电量,满足用户日常降噪使用需求。新能源发电监控的 FPGA 定制,保障发电设备稳定运行。学习FPGA定制项目代码

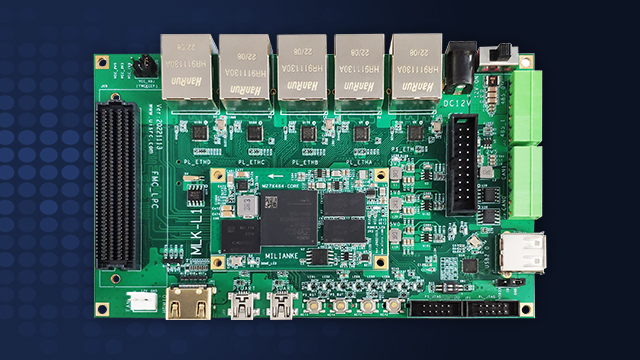

FPGA定制项目之通信路由器数据转发模块开发某网络设备公司需定制FPGA路由器数据转发模块,用于企业级路由器,要求支持10个千兆以太网端口,数据转发速率大于1Gbps,丢包率低于,且具备流量优先级管理功能。项目团队选用XilinxKintex-UltraScale系列FPGA,其高速数据处理与多端口扩展能力适配需求。FPGA接收各端口数据帧,通过路由表查找确定转发端口,结合优先级算法优先转发关键业务数据,同时进行数据校验防止错误传输。硬件设计优化信号完整性,支持端口扩展;软件层面实现流量统计,显示各端口负载。测试中,模块数据转发速率,丢包率,优先级管理可保障语音、视频数据优先传输,满足企业网络需求。 学习FPGA定制项目代码利用 FPGA 搭建数字信号处理流水线,快速处理复杂信号。

FPGA定制项目之工业激光切割控制模块开发某机械制造企业需定制FPGA激光切割控制模块,用于金属板材切割,要求切割精度误差小于,支持比较大×3m板材加工,切割速度根据板材厚度自动调整()。项目团队选用AlteraStratix10系列FPGA,其高速运动控制与脉冲输出能力适配激光切割需求。FPGA接收CAD设计的切割路径数据,通过轨迹规划算法生成运动指令,控制X、Y轴电机带动激光头移动,同时根据板材厚度数据调节激光功率与切割速度。硬件设计采用高速编码器接口,实时反馈电机位置;软件层面加入切割路径补偿算法,修正机械误差。测试中,模块切割圆形工件直径误差,切割矩形工件边长误差,不同厚度板材切割速度调整响应时间小于200ms,满足金属板材高精度切割需求。

FPGA定制项目之海洋环境监测数据采集模块开发某海洋科研机构需定制FPGA海洋环境监测模块,用于近海海域监测,要求采集水温、盐度、海流速度3项数据,采样间隔1小时,能承受水下50米压力,且支持无线数据传输。项目团队对比后选用MicrochipPolarFire系列FPGA,其耐水压特性与低功耗设计适配海洋场景。开发中,FPGA通过水下传感器采集环境数据,先对模拟信号进行抗干扰处理,再经ADC转换为数字量,通过低功耗无线模块将数据上传至浮标接收站。硬件设计采用防水密封外壳,加入压力补偿结构;软件层面设置数据缓存功能,避免传输中断导致数据丢失。测试阶段,在近海区域部署模块,水温检测误差±℃,盐度检测误差±‰,海流速度检测误差±,连续水下工作30天无故障,满足海洋科研监测需求。 FPGA 实现的电子密码锁系统,采用多重加密保障安全。

FPGA定制项目之医疗康复设备运动控制模块开发某医疗仪器公司需定制FPGA康复设备运动控制模块,用于下肢康复机器人,要求控制机械关节实现屈伸、旋转动作,动作角度范围0-120°,角度控制误差小于1°,且支持力度调节。项目团队选用AlteraArria10系列FPGA,其精细运动控制与安全保护能力符合医疗康复需求。FPGA接收康复师设定的运动参数,通过轨迹规划算法生成关节运动指令,控制伺服电机运转,同时通过力矩传感器监测运动力度,超出安全范围时自动减速。硬件设计加入紧急停止电路;软件层面支持多种康复模式预设。测试中,模块关节角度控制误差°,力度调节精度±,紧急停止响应时间小于200ms,可辅助患者进行下肢康复训练,满足医疗康复设备使用要求。 可穿戴医疗设备的 FPGA 定制,实现生理信号实时采集与分析。了解FPGA定制项目资料下载

基于 FPGA 的智能安防报警系统,能实时监测异常,迅速触发警报通知。学习FPGA定制项目代码

FPGA 定制项目之通信基站时钟同步模块开发某通信运营商需定制 FPGA 时钟同步模块,用于 5G 基站,要求支持 IEEE 1588 PTP 协议,时钟精度优于 10ns,且能抵抗网络抖动。项目团队选用具备高速 transceiver 的 Xilinx UltraScale 系列 FPGA,搭配高精度时钟芯片。FPGA 接收上级时钟源信号,通过 PTP 协议实现基站间时钟同步,采用数字锁相环技术消除网络抖动影响,输出稳定时钟信号至基站各模块。硬件设计优化时钟信号布线,减少相位噪声,软件层面加入时钟偏差校正算法,实时调整同步精度。测试中,模块时钟精度达 8ns,在网络抖动 100ms 的情况下仍保持同步稳定,满足 5G 基站信号传输时序要求。学习FPGA定制项目代码