- 品牌

- 桐尔

- 型号

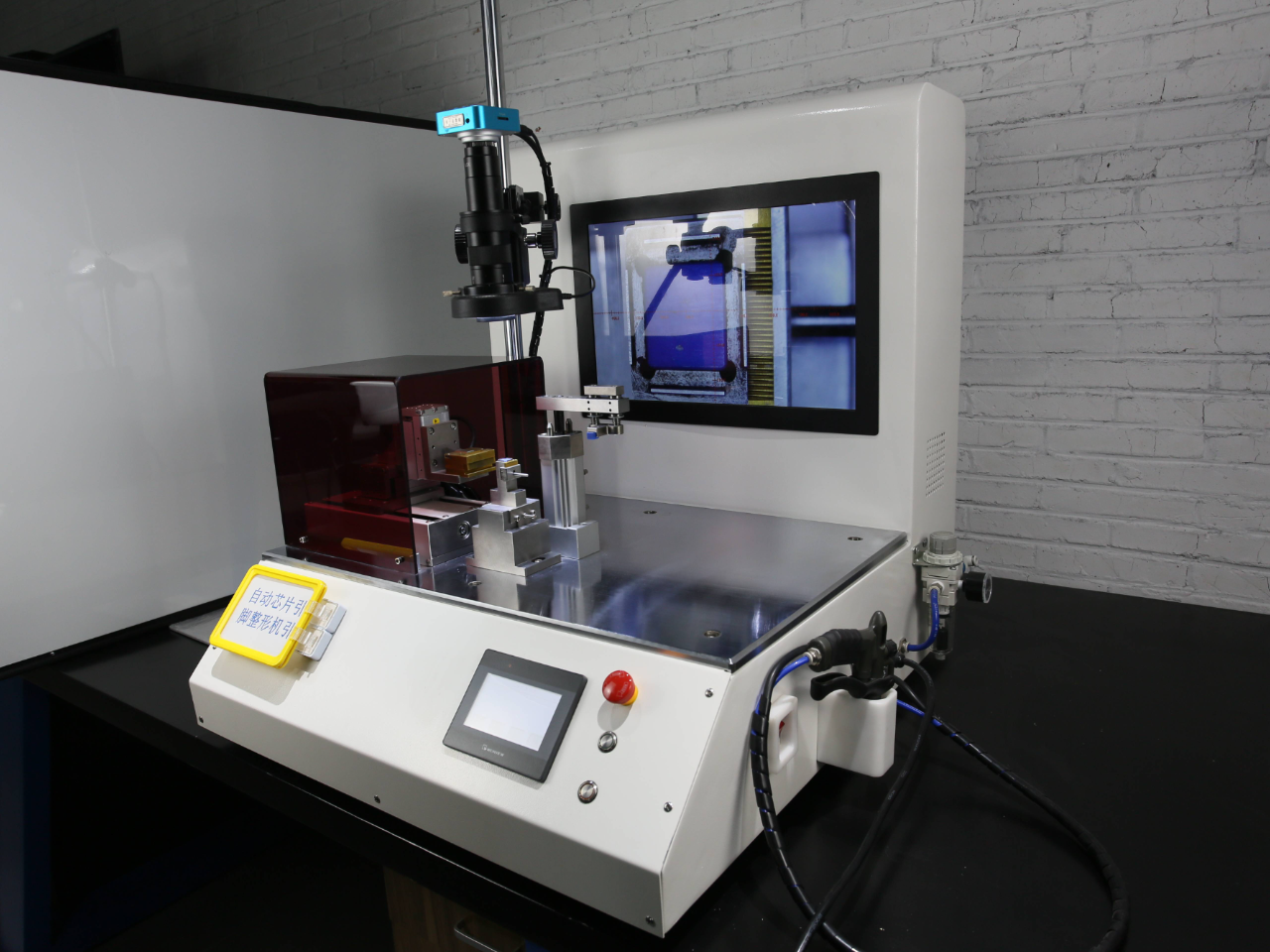

- TR-50S 芯片引脚整形机

该晶体管栅极包括第二层的第二部分并且搁置在***层的第二部分上。根据某些实施例,该电子芯片还包括第二电容部件,所述第二电容部件包括:所述半导体衬底中的第二沟槽;与所述第二沟槽竖直排列的第二氧化硅层;以及包括多晶硅或非晶硅的第三导电层和第四导电层,所述第二氧化硅层位于所述第三导电层和所述第四导电层之间并且与所述第三导电层和所述第四导电层接触,并且所述***氧化硅层和所述第二氧化硅层具有不同的厚度。根据某些实施例,该电子芯片还包括第二电容部件,所述第二电容部件包括:第三导电层和第四导电层;以及所述第三导电层和所述第四导电层之间的***氧化物-氮化物-氧化物三层结构。根据某些实施例,该电子芯片包括例如上文所定义的第二电容部件,***电容部件和第二电容部件的第二层和第三层是共用的,并且这些***层具有不同的厚度。根据某些实施例,该电子芯片包括附加的电容部件,该电容部件包括在第二层和第三层的附加部分之间的氧化物-氮化物-氧化物三层结构的***部分。根据某些实施例,该电子芯片包括存储器单元,所述存储器单元包括浮置栅极、控制栅极和位于所述浮置栅极和所述控制栅极之间的第二氧化物-氮化物-氧化物三层结构。上海桐尔的芯片引脚整形机,助力企业提升生产效率与产品质量。上海制造芯片引脚整形机厂家推荐

由于本发明提供的芯片引脚夹具阵列可灵活剪切为单个的芯片引脚夹具或包含一定芯片引脚夹具数量的芯片引脚夹具阵列,因此,*需生产制造足够长度的芯片引脚夹具阵列,即可满足多样化的使用需求。附图说明为了更清楚地说明本发明实施例的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。图1是本发明实施例提供的一种芯片引脚夹具100的结构示意图;图2是本发明实施例提供的一种壳体210的结构示意图;图3是本发明实施例提供的一种弹片320的结构示意图;图4是本发明实施例提供的一种芯片引脚夹具400的剖面示意图;图5是本发明实施例提供的一种芯片引脚夹具的工况示意图;图6是本发明实施例提供的另一种芯片引脚夹具的工况示意图;图7是本发明实施例提供的一种芯片引脚夹具夹持于芯片引脚的剖面示意图;图8是本发明实施例提供的一种芯片引脚夹具阵列800的结构示意图;图9是本发明实施例提供的一种芯片引脚夹具阵列的工况示意图;图10是本发明实施例提供的另一种芯片引脚夹具阵列的工况示意图。上海制造芯片引脚整形机厂家推荐半自动芯片引脚整形机可以与哪些软件或系统集成?

同时保持电容部件262和264中的至少一个电容部件。图3示出了电容式电子芯片部件300的实施例。电容部件300与图2的部件264相似,其中每个沟槽104由一个或多个沟槽302代替,层120、220和240的部分的堆叠覆盖沟槽302并且覆盖位于沟槽302之间并且在沟槽的任一侧上的衬底102的区域。层304使衬底区域与堆叠电绝缘。层304具有例如小于15nm量级,推荐。沟槽302使得它们的壁和它们的底部覆盖有电绝缘层305。沟槽填充有电导体,推荐掺杂多晶硅,电导体然后在每个沟槽302中形成通过绝缘层305与衬底分离的导电壁306。例如,层305具有层304厚度量级中的厚度。沟槽302推荐具有在从300nm至600nm的范围中的深度。沟槽推荐具有在从μm至μm的范围中的宽度。层120例如通过绝缘层部分320与壁306分离。然后将壁306和层120连接在一起(连接330)。作为变型,层120与壁306接触。层120和壁306耦合到、推荐地连接到电容部件300的端子a。推荐地,沟槽302界定衬底102的p型掺杂区域310。区域310推荐地位于共同的n型掺杂区域312上。沟槽302到达、推荐地穿透到区域312中,使得区域310彼此电绝缘。区域310耦合到电容部件300的端子b。上层240耦合到端子b。因此对于相同占据的表面积。

可替换针床测试机SPEA**测试机能够轻松地代替原有针床的批量性生产;每小时80片的测试量,每年超过,包含4块单板,950个节点,700个元器件;微小pad接触可靠性探针接触的精细性允许我们的设备能可靠地接触微小的SMD原件,Probe卡的连接PIN,G公/母头连接器(如:背板测试);**小50um尺寸的pad,能达到10μm探测的精度;无需花费治具费用对于SPEA的**测试机,客户可以省掉以下所有相关费用;治具的开发制作,在产品研发阶段的实验室测试(SPEA**是随时准备好可以进行测试)如果有多条生产线则治具倍增;若产品的layout改变,治具将不得不重新设计,治具维护和周期替换将被节省;减少市场返修SPEA测试机有能力量测在线电路的关键部件的主要参数(如电源器件、传感器器件、传动器件),有效识别不良器件(导致过早损坏)有效减少市场返修;早期故障发现减少了后续阶段/后制程的经济损失简化了功能测试设备,减少了功能测试时间;精细的微小SMD植针微型化不会止步且SPEA的**设备已经为未来做足准备。每个X-Y-Z轴上的线性光学编码器使得精细的定位成为可能,该项技术提供了探针实时位置的反馈,在XYZ轴上的高性能线性光学编码器微型-SWD(008004)pad精细接触灵活/轻薄的印制电路可靠的测试。 每日开机前点检伺服压力、每周巡检吸嘴磨损,可让半自动芯片引脚整形机保持好状态。

上海桐尔在为华东地区某SMT产线提供自动化搪锡解决方案时发现,因引脚设计不合理导致的返修成本占总生产成本的23%。该公司的工程数据显示,引脚接触不良引发的故障平均需要4.7小时/台的维修时间,而采用其全自动搪锡机配合优化后的引脚设计方案后,良品率从82%提升至98.6%。上海桐尔的成本分析报告显示,合理的引脚设计可以降低三大**成本:材料成本(减少贵金属镀层厚度)、加工成本(缩短搪锡时间30%)和质量成本(降低售后索赔率)。该公司为客户提供的引脚设计咨询服务,已累计节省生产成本超过2800万元。特别是在半导体封装领域,通过采用上海桐尔创新的"梯度引脚"设计方案,客户在BGA封装项目上实现了单颗芯片成本下降15%的突破。这些实践表明,前期的引脚设计投入可以带来***的全生命周期成本优势。上海桐尔TR-50S芯片引脚整形机采用多轴联动技术,精度达±0.01mm,提升半导体封装良率至99.8%。上海制造芯片引脚整形机厂家推荐

桐尔芯片整形机闭环压力控制,保护引脚镀层,良品率达99.2%。上海制造芯片引脚整形机厂家推荐

沟槽填充有电绝缘层,例如氧化硅。沟槽推荐地完全填充有绝缘层。推荐地,在填充之后,去除绝缘层位于沟槽外部的部分。位于沟槽中的绝缘体部分106可以与衬底102的前表面齐平。作为变型,这些部分的顶部位于衬底102的前表面上方。如图1b-图2c所示方法接下来的步骤s2至s6旨在形成位于沟槽104的绝缘体106上的相应部分c1、c2和c3中的电容部件。推荐地,在位于由沟槽104界定的衬底区域上的部分m1、t2和t3中,步骤s2至s6进一步旨在形成:-在部分m1中,由***栅极绝缘体隔开的、存储器单元的浮置栅极和控制栅极的堆叠;-在部分t2中,由第二栅极绝缘体绝缘的晶体管栅极;以及-在部分t3中,由第三栅极绝缘体绝缘的晶体管栅极。在步骤s2至s6期间形的元件*在电子芯片的部分c1、c2、c3、m1、t2和t3中示出。未描述位于部分c1、c2、c3、m1、t2和t3之外的元件的形成和可能的移除,并且基于本说明书在本领域技术人员的能力内,这里描述的步骤与通常的电子芯片制造方法是兼容的。在图1b所示的步骤s2中,在步骤s1中获得的结构上形成包括多晶硅或非晶硅的导电层120。硅推荐包括晶体,该晶体在平行于前表面的方向上具有小于约200nm、例如200nm或小于层120的厚度的尺寸。上海制造芯片引脚整形机厂家推荐

1:焊锡结合强度的可视化通过该款机型独有的3D-CT再构建算法,以高一致性的重复精度,再现**度焊锡所需的锡脚形状。通过对焊锡形状等实装状态的量化检查,实现符合行业规格的品质检查,使漏检风险达到较小,并且在生产切换时实现迅速稳定的品质对应。2:设计变更不受制约伴随基板的小型化,当设计变更需要实现高密度实装、层叠实装等情况时,使用3D-CT式X-ray实现生产验证,使设计变更方案不再因生产工艺得不到验证而受到制约3:产品被辐射量减少)高速摄像技术在保证检查画质的同时,通过高速摄像技术,减少辐射。)X线源在装置下端大部分实装基板都会把重要元件设计在TOP面。由于线源自下而上照射,物理层...

- 通用芯片引脚整形机作用 2025-11-28

- 南京本地芯片引脚整形机哪家好 2025-11-26

- 上海制造芯片引脚整形机厂家推荐 2025-10-22

- 南京库存芯片引脚整形机售后服务 2025-08-27

- 江苏自动芯片引脚整形机联系方式 2025-08-26

- 江苏通用芯片引脚整形机作用 2025-02-19

- 上海台式芯片引脚整形机技巧 2024-05-06

- 南京本地芯片引脚整形机哪家好 11-26

- 上海制造芯片引脚整形机厂家推荐 10-22

- 北京哪里有搪锡机设计 10-15

- 南京库存芯片引脚整形机售后服务 08-27

- 江苏自动芯片引脚整形机联系方式 08-26

- 湖南小型全自动点胶机产品介绍 07-02

- 广东直销汽相回流焊接导热液多少钱 06-17

- 常规JC736-CS钢网清洗机设备厂家 06-10

- 附近哪里有超景深显微镜服务 05-09

- 苏州使用全自动半钢电缆成型系统价格 04-07