COB的理论优势1、设计研发:没有了单个灯体的直径,理论上可以做到更加微小。2、技术工艺:减少支架成本和简化制造工艺,降低芯片热阻,实现高密度封装。3、工程安装:从应用端看,COBLED显示模块可以为显示屏应用方的厂家提供更加简便、快捷的安装效率。4、产品特性上:超轻薄:可根据客户的实际需求,采用厚度从0.4-1.2mm厚度的PCB板,使重量极少降低到原来传统产品的1/3,可为客户明显降低结构、运输和工程成本。防撞抗压:COB产品是直接将LED芯片封装在PCB板的凹形灯位内,然后用环氧树脂胶封装固化,灯点表面凸起成球面,光滑而坚硬,耐撞耐磨。大视角:视角大于175度,接近180度,而且具有更的光学漫散色浑光效果。5G 芯片对封装要求高,中清航科定制方案,适配高速传输场景需求。江苏第三代半导体封装

中清航科WLCSP测试一体化方案缩短生产周期。集成探针卡与临时键合层,实现300mm晶圆单次测试成本降低40%。在PMIC量产中,测试覆盖率达99.2%。面向航天应用,中清航科抗辐照封装通过MIL-STD-750认证。掺铪二氧化硅钝化层使总剂量耐受>300krad,单粒子翻转率<1E-10error/bit-day。已服务低轨卫星星座项目。中清航科MEMS真空封装良率突破98%。采用多孔硅密封技术,腔体真空度维持<0.1Pa十年以上。陀螺仪零偏稳定性达0.5°/h,满足导航级应用。江苏TO220封装存储芯片封装求快求稳,中清航科接口优化,提升数据读写速度与稳定性。

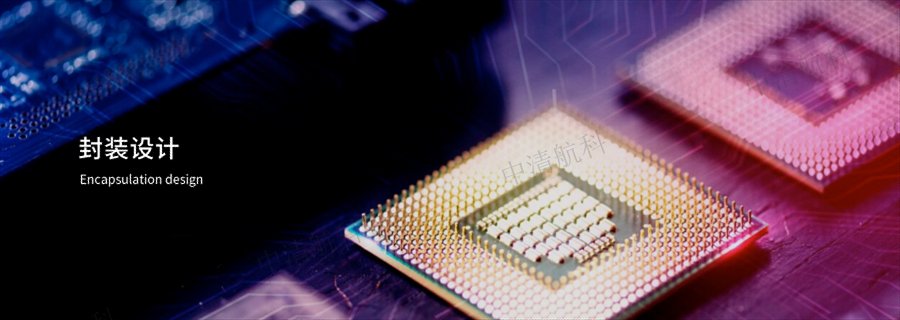

随着摩尔定律逼近物理极限,先进封装成为提升芯片性能的关键路径。中清航科在Fan-Out晶圆级封装(FOWLP)领域实现突破,通过重构晶圆级互连架构,使I/O密度提升40%,助力5G射频模块厚度缩减至0.3mm。其开发的激光解键合技术将良率稳定在99.2%以上,为毫米波通信设备提供可靠封装方案。面对异构集成需求激增,中清航科推出3DSiP立体封装平台。该方案采用TSV硅通孔技术与微凸点键合工艺,实现CPU、HBM内存及AI加速器的垂直堆叠。在数据中心GPU领域,其散热增强型封装结构使热阻降低35%,功率密度提升至8W/mm²,满足超算芯片的严苛要求。

常见芯片封装类型-DIP:DIP即双列直插式封装,是较为早期且常见的封装形式。它的绝大多数中小规模集成电路芯片采用这种形式,引脚数一般不超过100个。采用DIP封装的芯片有两排引脚,可插入具有DIP结构的芯片插座,也能直接焊接在有对应焊孔的电路板上。其优点是适合PCB上穿孔焊接,操作方便;缺点是封装面积与芯片面积比值大,体积较大。中清航科在DIP封装业务上技术成熟,能以高效、稳定的生产流程,为对成本控制有要求且对芯片体积无严苛限制的客户,提供质优的DIP封装产品。中清航科聚焦芯片封装,用仿真预判风险,缩短研发验证周期。

为应对Chiplet集成挑战,中清航科推出自主知识产权的混合键合(HybridBonding)平台。采用铜-铜直接键合工艺,凸点间距降至5μm,互连密度达10⁴/mm²。其测试芯片在16核处理器集成中实现8Tbps/mm带宽,功耗只为传统方案的1/3。中清航科研发的纳米银烧结胶材料突破高温封装瓶颈。在SiC功率模块封装中,烧结层导热系数达250W/mK,耐受温度600℃,使模块寿命延长5倍。该材料已通过ISO26262认证,成为新能源汽车OBC充电模组优先选择方案。中清航科芯片封装团队,攻克精密焊接难题,保障芯片内部连接稳定。浙江陶瓷封装厂家

芯片封装防干扰至关重要,中清航科电磁屏蔽技术,保障复杂环境稳定。江苏第三代半导体封装

中清航科的技术合作与交流:为保持技术为先,中清航科积极开展技术合作与交流。公司与国内外高校、科研院所建立产学研合作关系,共同开展芯片封装技术研究;参与行业技术研讨会、标准制定会议,分享技术经验,了解行业动态。通过技术合作与交流,公司不断吸收先进技术和理念,提升自身技术水平,为客户提供更质优的技术服务。芯片封装的失效分析与解决方案:在芯片使用过程中,可能会出现封装失效的情况。中清航科拥有专业的失效分析团队,能通过先进的分析设备和技术,准确找出封装失效的原因,如材料缺陷、工艺问题、使用环境不当等。针对不同的失效原因,公司会制定相应的解决方案,帮助客户改进产品设计或使用方式,提高产品可靠性,减少因封装失效带来的损失。江苏第三代半导体封装