FPGA开发板丰富的外设接口极大拓展了其应用边界。通用输入输出接口(GPIO)具有高度灵活性,通过编程可配置为输入或输出模式,用于连接各类传感器与执行器。例如,连接温度传感器可采集环境温度数据,连接LED灯可实现不同的灯光显示效果。UART接口实现了开发板与其他设备之间的串行通信,常用于数据传输与指令交互场景,如与计算机进行数据通信,将开发板采集到的数据上传至计算机进行分析。SPI和I²C接口则适用于与外部芯片进行高速稳定的数据通信,可连接EEPROM、ADC等芯片。此外,以太网接口使开发板具备网络通信能力,能够接入局域网或互联网,在物联网应用中,实现设备间的数据交互与远程数据传输,这些多样化的接口让FPGA开发板能够适应多种复杂的应用环境。FPGA 开发板高速接口支持高带宽传输。辽宁MPSOCFPGA开发板工程师

FPGA开发板的功耗管理是开发者需要关注的重要方面。在便携式设备或电池供电的应用场景中,降低开发板功耗尤为关键。开发者可通过优化FPGA逻辑设计,减少不必要的逻辑翻转,降低芯片动态功耗。合理配置开发板外设,在不使用时将其设置为低功耗模式,进一步降低系统功耗。部分开发板提供专门的功耗管理模块,帮助开发者监控与调节功耗,通过软件设置实现不同的功耗管理策略。良好的功耗管理使FPGA开发板能够在低功耗状态下稳定运行,满足特定应用场景对功耗的严格要求,延长设备续航时间。浙江XilinxFPGA开发板套件FPGA 开发板时钟模块提供可配置频率信号。

FPGA开发板在电子竞赛领域展现出独特优势。电子竞赛题目往往对硬件的灵活性与功能实现有较高要求,FPGA开发板凭借其可编程特性,能够快速响应不同竞赛需求。在智能车竞赛中,参赛团队使用开发板处理传感器采集到的赛道信息,如光电传感器检测赛道黑线、陀螺仪获取车身姿态数据等。通过编写相应算法对数据进行分析处理,进而驱动电机实现智能车在赛道上的行驶。在电子设计竞赛中,开发板可用于实现信号处理、数据采集、无线通信等多个功能模块,满足竞赛题目多样化的需求。参赛者通过对开发板的不断编程与调试,优化系统性能,提升作品竞争力,使FPGA开发板成为电子竞赛中不可或缺的开发平台。

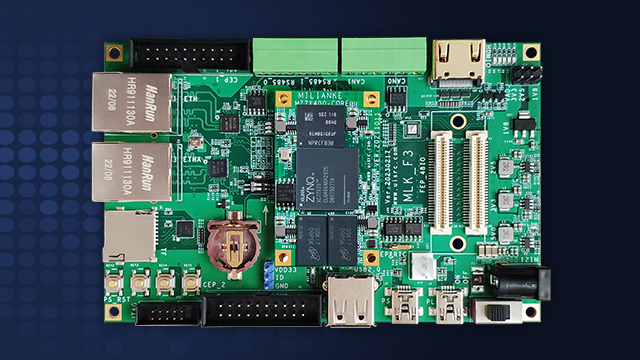

米联客MIZ702NFPGA开发板(Zynq-7020款)米联客MIZ702N开发板基于XilinxZynq-7020芯片设计,聚焦嵌入式系统入门与轻量型应用开发。该芯片集成双核ARMCortex-A9处理器与28nmFPGA逻辑资源(28万逻辑单元),兼顾软件控制与硬件加速能力。硬件配置上,开发板搭载512MBDDR3内存、16GBeMMC闪存,板载HDMI输出接口、USBOTG接口、千兆以太网接口及40针扩展接口,可连接摄像头、显示屏等外设,搭建完整嵌入式应用场景。软件支持方面,开发板适配Vitis开发环境与Petalinux操作系统,提供基础Linux镜像与驱动源码,用户可快速实现“处理器+FPGA”协同开发。配套资料包含多个入门案例,如HDMI图像显示、以太网数据传输、GPIO控制等,每个案例附带详细步骤说明与代码注释。该开发板尺寸为12cm×10cm,采用沉金工艺提升接口耐用性,适合嵌入式爱好者入门实践,也可作为高校嵌入式课程的教学实验平台,帮助用户掌握软硬件协同设计思路。 FPGA 开发板电源指示灯显示供电状态。

FPGA开发板在金融领域的应用逐渐兴起,为金融科技的发展带来新的机遇。在高频交易系统中,时间就是金钱,对数据处理速度和实时性要求极高。FPGA开发板凭借其高速并行处理能力,能够快速获取金融市场的实时行情数据,如价格、汇率、期货价格等。通过预先编写的交易算法,开发板对这些数据进行实时分析和处理,在极短的时间内做出交易决策,并执行交易指令。与传统的基于CPU的交易系统相比,FPGA开发板能够缩短交易延迟,提高交易效率,帮助金融机构在激烈的市场竞争中抢占先机。同时,开发板的可重构特性使得金融机构能够根据市场变化和交易策略的调整,快速对交易算法进行修改和优化,实现交易系统的灵活升级,更好地适应复杂多变的金融市场环境,提升金融交易的智能化和高效化水平。FPGA 开发板示例代码注释清晰便于学习。山东XilinxFPGA开发板学习步骤

FPGA 开发板网络接口支持远程调试。辽宁MPSOCFPGA开发板工程师

1.FPGA开发板的时钟模块作用时钟信号是FPGA数字逻辑设计的“脉搏”,开发板上的时钟模块通常由晶体振荡器、时钟缓冲器和时钟分配网络组成。晶体振荡器能提供高精度的固定频率信号,常见频率有25MHz、50MHz、100MHz等,部分板卡还会集成可配置的时钟发生器,支持通过软件调整输出频率,满足不同算法对时钟周期的需求。时钟缓冲器可将单一时钟信号复制为多路同步信号,分配给FPGA内部的不同逻辑模块,避免因信号延迟导致的时序偏差。在高速数据处理场景中,如图像处理或通信信号解调,时钟模块的稳定性直接影响数据采样精度和逻辑运算的同步性,因此部分开发板还会加入时钟抖动抑制电路,进一步降低信号噪声。辽宁MPSOCFPGA开发板工程师